CMOS模擬集成電路設計基礎與HSPICE學習記錄

CMOS模擬集成電路設計是當今微電子領域的核心技術之一,廣泛應用于通信、消費電子、醫(yī)療設備等領域。艾倫的課件為我們系統(tǒng)學習這一領域提供了寶貴的指引,而HSPICE作為行業(yè)標準的電路仿真工具,則是將理論轉化為實踐的關鍵橋梁。

一、CMOS模擬集成電路基礎

CMOS技術因其低功耗、高集成度和良好的工藝兼容性,已成為現(xiàn)代集成電路的主流。模擬集成電路設計主要處理連續(xù)變化的信號,其核心在于理解并利用MOS晶體管的特性。基礎部分通常涵蓋:

- MOSFET物理與模型:深入理解MOS管在飽和區(qū)、線性區(qū)和截止區(qū)的工作特性,以及小信號模型,是設計的基石。

- 單級放大器:包括共源、共柵、共漏(源極跟隨器)及其組合(如共源共柵)結構,分析其增益、帶寬、輸入輸出阻抗等關鍵性能指標。

- 差分放大器與電流鏡:這是模擬電路的核心模塊,用于提供高共模抑制比、實現(xiàn)偏置和作為有源負載。

- 頻率響應與反饋理論:分析電路的穩(wěn)定性、帶寬,并運用反饋技術來精確控制增益、線性度等性能。

- 運算放大器設計:作為典型的模擬系統(tǒng),其設計綜合了偏置、增益級、輸出級和頻率補償?shù)燃夹g。

二、HSPICE學習實踐記錄

理論學習需通過仿真來驗證和深化。HSPICE學習通常從以下步驟開始:

- 網表編寫:學習使用HSPICE語法描述電路拓撲、器件參數(shù)(如MOS管的W/L)、電源、激勵信號和仿真控制語句。這是與仿真器溝通的語言。

- 直流工作點分析(.OP):用于檢查晶體管是否工作在預期的區(qū)域(如飽和區(qū)),并獲取偏置電壓、電流等靜態(tài)信息。

- 直流掃描分析(.DC):用于分析電路傳輸特性,如放大器的電壓轉移曲線,或晶體管的I-V特性曲線。

- 瞬態(tài)分析(.TRAN):觀察電路在時域中對輸入信號(如正弦波、脈沖)的響應,是評估時域性能(如建立時間、擺率)的主要手段。

- 交流小信號分析(.AC):在直流工作點線性化的基礎上,分析電路的頻率響應(幅頻/相頻特性),獲取增益、帶寬、相位裕度等關鍵AC指標。

- 噪聲與工藝角分析:通過

.NOISE分析評估電路噪聲性能,通過.ALTER或工藝角模型(TT, FF, SS等)評估設計在工藝、電壓、溫度變化下的魯棒性。

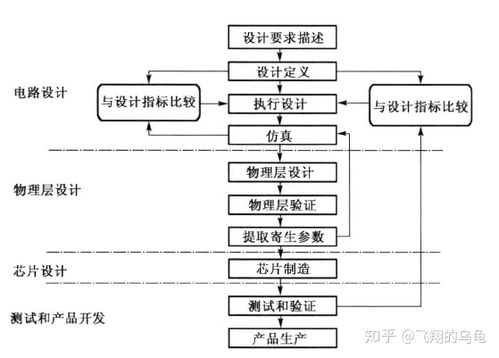

三、集成電路設計流程

結合理論與工具,一個完整的模擬IC設計流程大致為:

- 指標定義:根據(jù)系統(tǒng)需求,明確性能指標(增益、帶寬、功耗、面積等)。

- 電路拓撲選擇與手工計算:基于理論選擇合適架構,并進行初步的手工分析與器件尺寸估算。

- HSPICE仿真與迭代優(yōu)化:將初步設計的網表輸入HSPICE,通過各類仿真驗證性能,并與指標對比。不斷調整器件參數(shù)、優(yōu)化結構,直至滿足所有要求。此過程是設計的核心循環(huán)。

- 版圖設計與后仿真:將電學原理圖轉化為物理版圖,并提取包含寄生參數(shù)的網表進行后仿真,確保實際制造出的芯片性能符合預期。

- 流片與測試:完成設計后交付制造,并對芯片樣品進行實際測試。

掌握CMOS模擬集成電路設計原理是根本,熟練運用HSPICE進行仿真驗證與優(yōu)化是關鍵。通過系統(tǒng)學習艾倫課件中的基礎知識,并持之以恒地進行HSPICE仿真實踐,將能逐步構建起扎實的設計能力,為應對更復雜的模擬及混合信號系統(tǒng)設計挑戰(zhàn)打下堅實基礎。

如若轉載,請注明出處:http://www.wxred.cn/product/77.html

更新時間:2026-01-19 05:49:28